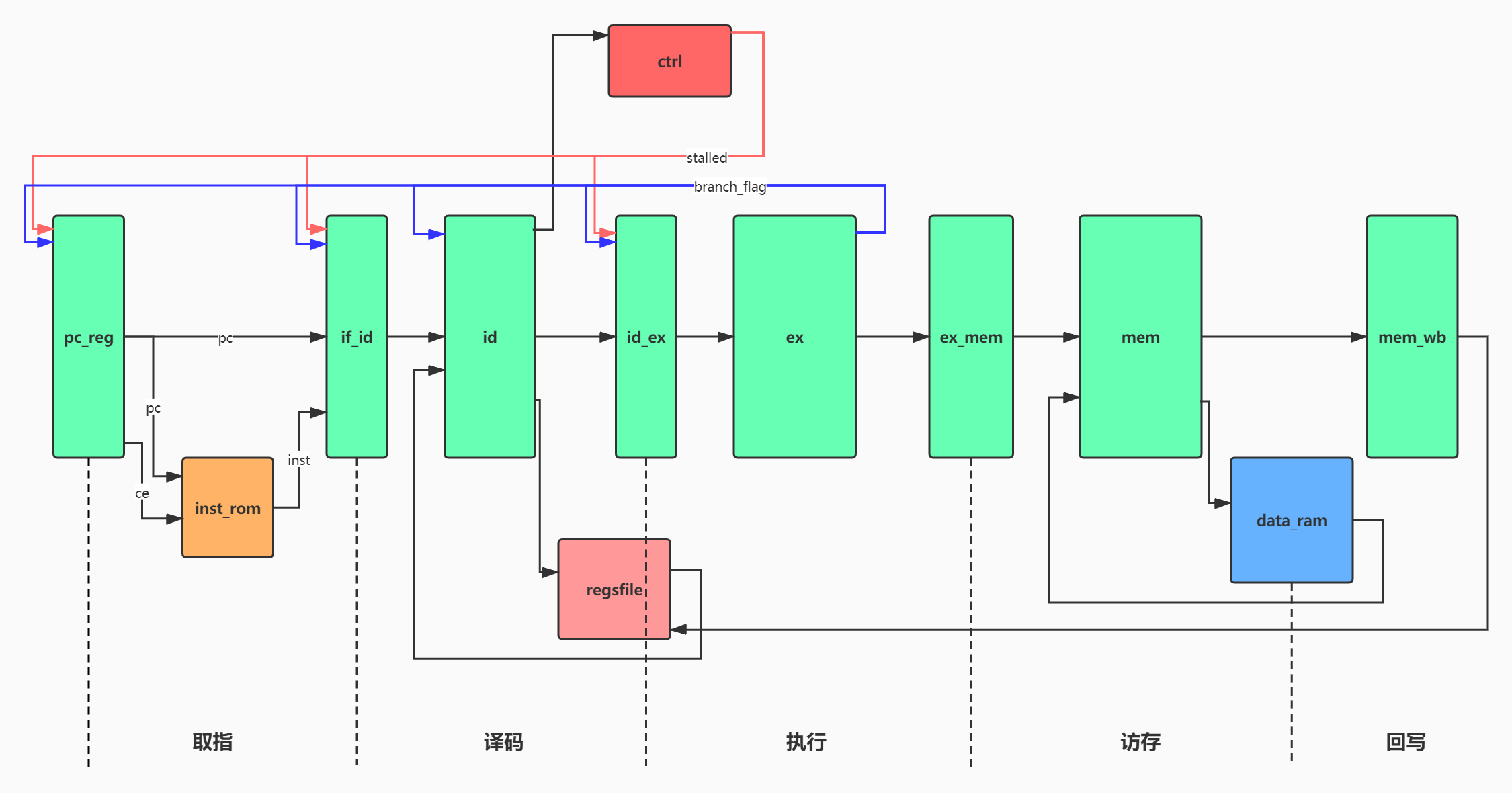

bittyCore 是采用 Verilog 语言编写的 32 位 RISC-V 内核,支持 RV32I 指令集和 5 级流水线。

bittyCore 已完成模型联合仿真测试,并通过了 RISC-V 官方 RV32I ISA 指令集测试。

项目目录说明:

├─rtl

│ ├─core # bittyCore verilog 源码

│ └─sim # 仿真顶层文件及目录

├─tests

│ └─example

│ └─simple # 简单测试工程代码

└─tools # Windows 和 Linux 下的仿真脚本文件以及 filelist克隆项目并进入项目文件夹

git clone https://github.com/strongwong/bittyCore_RISC-V.git

cd bittyCore_RISC-V

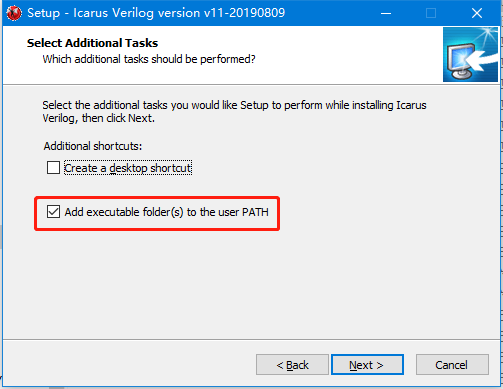

在 windows 下安装 iverilog, 下载地址:http://bleyer.org/icarus/

安装时选择将执行文件夹添加到环境变量

执行仿真脚本

.\tools\build.bat仿真完成后可以使用 gtkwave 查看仿真波形

gtkwave .\rtl\sim\bitty_riscv_sopc_tb.vcd % or gtkwave .\rtl\sim\bitty_riscv_sopc_tb.gtkw %ubuntu:

安装 iverilog

sudo apt update

sudo apt install iverilog执行仿真脚本

chmod +x ./tools/build.sh

./tools/build.sh仿真完成后使用 gtkwave 查看波形

sudo apt install gtkwave

gtkwave ./rtl/sim/bitty_riscv_sopc_tb.vcd # or gtkwave ./rtl/sim/bitty_riscv_sopc_tb.gtkwbittyCore is powered by VeriMake