-

Notifications

You must be signed in to change notification settings - Fork 69

SystemVerilog IO descriptions

Descriptions of both the processor-facing and internal-facing IO ports in the generated RTL output are shown below.

Ordt generates the following decoder module IO that will be driven by processor logic. Several processor interface forms are currently supported: parallel, leaf, ring8, ring16, ring32, and serial8. The type can be specified via the root_decoder_interface ordt parameter for systemverilog output.

The parallel interface type provides N bit parallel data buses for read/write data transfer. The data width is determined by the largest register in the region being addressed. Specify using root_decoder_interface = parallel.

* IO direction is shown for the primary processor interface on a generated decoder. An complementary interface form with inverted IO direction will be generated for register/regfile regions instanced using external(PARALLEL) - see here for more info. In this mode, the interface would typically drive a child addrmap module using a parallel processor interface.

Also note that IO names in the table above reflect the case where a child decoder is being driven by a parent decoder interface (thus the reg path is included in the names). In the root decoder, simplified names will be used, eg. h2d_pio_dec_read, h2d_pio_dec_write, h2d_pio_dec_address, h2d_pio_dec_write_data, d2h_dec_pio_read_data, d2h_dec_pio_ack, d2h_dec_pio_nack, etc.

The parallel_pulsed interface type is identical to the parallel type, except that input signals for initiating a read or write (h2d_<regname>_re, h2d_<regname>_we) expect a single cycle pulse high rather than remaining high until an ack/nack response. Specify using root_decoder_interface = parallel_pulsed.

The leaf interface type provides N bit parallel data buses for read/write transfer. Specify using root_decoder_interface = leaf.

The serial8 interface type provides a 8 bit data buses for read/write transfer. Specify using root_decoder_interface = serial8.

* IO direction is shown for the primary processor interface on a generated decoder. An complementary interface form with inverted IO direction will be generated for register/regfile regions instanced using external(SERIAL8) - see here for more info. In this mode, the interface would typically drive a child addrmap module using a serial8 processor interface.

The ring8 interface type provides a 8 bit data buses for read/write transfer to multiple child decoders. Specify using root_decoder_interface = ring8.

* IO direction is shown for the primary processor interface on a generated decoder. An complementary interface form with inverted IO direction will be generated for register/regfile regions instanced using external(RING8) - see here for more info. In this mode, the interface would typically drive a child addrmap module(s) using a ring8 processor interface.

The ring16 interface type provides a 16 bit data buses for read/write transfer to multiple child decoders. Specify using root_decoder_interface = ring16.

* IO direction is shown for the primary processor interface on a generated decoder. An complementary interface form with inverted IO direction will be generated for register/regfile regions instanced using external(RING16) - see here for more info. In this mode, the interface would typically drive a child addrmap module(s) using a ring16 processor interface.

The ring32 interface type provides a 32 bit data buses for read/write transfer to multiple child decoders. Specify using root_decoder_interface = ring32.

* IO direction is shown for the primary processor interface on a generated decoder. An complementary interface form with inverted IO direction will be generated for register/regfile regions instanced using external(RING32) - see here for more info. In this mode, the interface would typically drive a child addrmap module(s) using a ring16 processor interface.

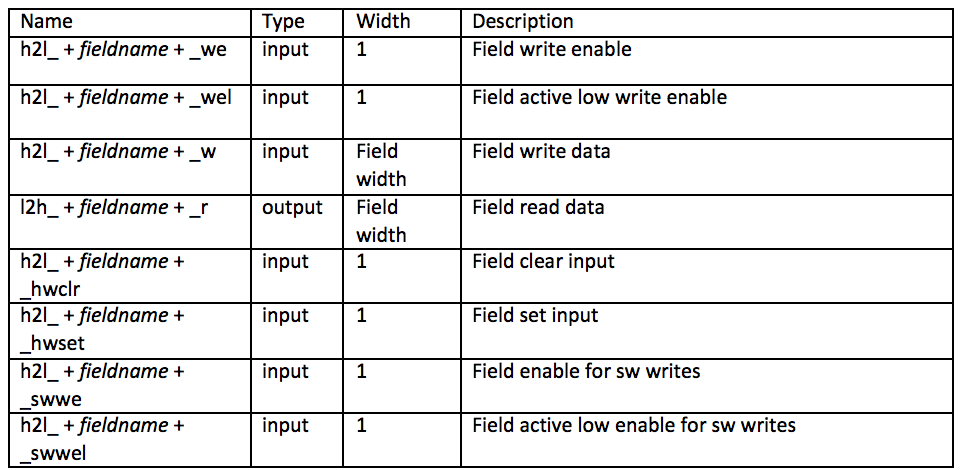

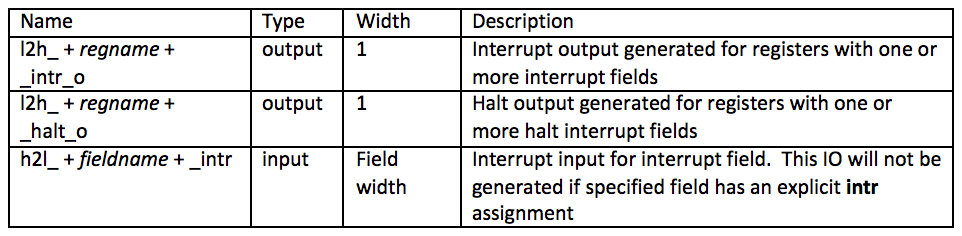

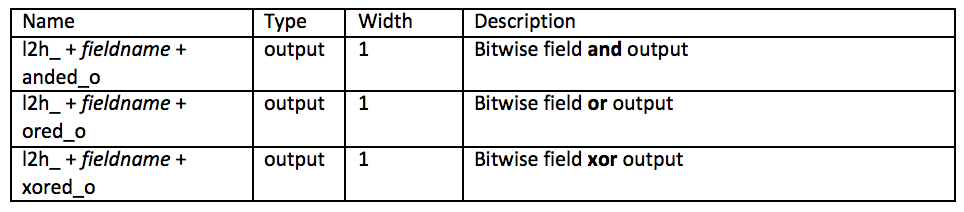

Ordt generates the following logic module IO for passing register and field information to user RTL. All of the following signals are optional and depend on the SystemRDL properties specified.

Home

Running Ordt

Building Ordt from source

Running Ordt Tests

Source contributions

Ordt Inputs

Ordt Outputs