-

Notifications

You must be signed in to change notification settings - Fork 69

Using SystemRDL input

The Ordt tool supports an implementation of the SystemRDL v1.0 Register Description Language for describing and generating registers. Rdl allows complex register structures such as counters and interrupt schemes to be described. Information on SystemRDL can be found at http://accellera.org/downloads/standards/systemrdl.

Some SystemRDL examples can be found here as well as in the test area.

- SystemRDL features not implemented

- Ordt syntax differences vs SystemRDL

- Ordt property extensions to SystemRDL

Several SystemRDL features are not implemented in the current version Ordt. These include:

-

Selection of addressing modes (compact, regalign, fullalign). Ordt addresses are generated in fullalign mode (registers/regfiles aligned on next 2^n byte boundary of their size) which is consistent with Jspec. regalign mode can optionally be enabled by setting the global use_js_address_alignment parameter to false. However, it is recommended that the default fullalign mode be used where possible as some output formats (jspec, xml) assume use of fullalign addresses.

-

Selection of endianness/bit order. littleendian and lsb0 modes are assumed.

-

User defined reference properties. Ordt supports numeric, string, and boolean user defined properties. To avoid name collisions, user property names should begin with p_, though this can be overridden by the restrict_defined_property_names rdl input parameter. Currently, user defined property values are included in generated xml and uvmregs output.

-

Overlapping/alias field definitions for a register

-

Perl and verilog RDL preprocessors as defined in the SystemRDL 1.0 standard. Beyond the basic verilog and C preprocessors, there are a variety of perl and python based file preprocessor tools available to perform this function (see here).

The following SystemRDL keywords are not currently supported by Ordt:

arbiter addressing clock sync async

sharedextbus errextbus littleendian bigendian rsvdset

rsvdsetX bridge shared msb0 lsb0

internal alignment accesswidth

Ordt includes the following extensions/changes relative to SystemRDL v1.0 syntax:

For example, the wildcard below will set the hw property to rw for all fields in register status:

int_status_reg status;

status.*->hw = rw;

The wildcard below will set the enable property of each field in interrupt register status to the same-named field in register enable_reg:

status.*->enable = enable_reg.*;

Note: Use of field wildcards assumes field names and bit widths are appropriate for the specified assignment

For example, the following code sets nonsticky intr properties on register poll:

int_status_reg poll;

poll.*->intr = true;

poll.*->nonsticky = true;

The root addrmap in a SystemRDL file must be explicitly instanced (unless the process_component rdl input parameter is specified)

For example,

addrmap a_map {

a_regfile_common com @0x0;

a_regfile_stats stats @0x2000;

a_regfile_inp inp @0x100000;

a_regfile_rdr rdr @0x300000;

a_regfile_psv psv @0x400000;

} root_map_name; // <--- need an instanced addrmap at root for RTL generation

Ordt supports escaped instance and component names to allow use of rdl reserved keywords. For example:

reg \enable;

Ordt adds an address shift operator (>>) to allow creation of gaps in the address space. For example, the code below will create a 4 Byte gap between registers foo and bar:

reg foo;

reg bar >>0x4;

The external_decode keyword is added to identify external address regions that are not accessible by the ordt generated decoder (ie, the address region will be a hole in the generated decoder map)

External interface type support is added to allow a variety of rtl connectivity options for external register regions, The type is specified using syntax external(TYPE <options>). For example,

myRegset int_regs @0x0; // this register set is internal

external myRegset default_ext_regs @0x1000; // this register set will be accessed by a default external interface (PARALLEL)

external(RING16 dly=2) myRegset ring_ext_regs @0x2000; // this register set will be accessed by a RING16 external interface with 2 added delay stages

Currently allowed values of type are:

PARALLEL – parallel data read/write interface.

Options:

-

opt=(YES|NO|KEEP_NACK, default NO) - determines if external IO will be optimized to remove unnecessary ports based on register read/write access settings (ie, if sw read-only, no write IO are added). For designs with hierarchical decoders attached to an external interface it is generally necessary to retain all IOs (ie opt=NO). Default behavior for optimization is set by the optimize_parallel_externals systemverilog output parameter. The KEEP_NACK option will optimize all IO as appropriate except nack.

-

field_data=(YES|NO, default NO, added 180605.01) - if YES, the external interface of a register region will include separate signals for each field in the register rather than a register wide signal for read and write data. This option only applies to external registers, not regfiles.

-

rep_level=N (default 0, added 180605.01) - if non-zero, a single external interface will be generated for N levels of the register region's replicated parent regfiles. The parent indices being accessed will be reflected as additional msbs of the address signal on the combined interface. If parent regfiles have non-power-2 replication counts, the user is responsible for generating a nack should an invalid parent index (beyond max) be accessed. Also note that uvmregs model output for this rdl form is not able to model replicated regfiles using uvm_mem, which can be an issue for large parent replication counts. Example use:

regfile { regfile { external(PARALLEL) myReg32 extregs1[16]; // create 32 external interfaces, each with 4b address external(PARALLEL rep_level=1) myReg32 extregs2[16]; // create 8 external interfaces, each with 6b address external(PARALLEL rep_level=2) myReg32 extregs3[16]; // create 1 external interface with 9b address } level1[4]; } level2[8];

BBV5_16 – interface to pio version 5 backbone root module supporting 16b data rings

SRAM – simplified interface supporting only a single data width and contiguous addresses

SERIAL8 – 8 bit point to point data interface.

Options:

- dly=N - sets the number of additional delay stages that will be added to/from master.

RING8 – 8 bit ring interface.

Options:

- dly=N (default 0) - sets the number of additional delay stages that will be added to/from the ring master. Note that inter-node ring delay is set by the ring_inter_node_delay systemverilog output parameter.

RING16 – 16 bit ring interface.

Options:

- dly=N (default 0) - sets the number of additional delay stages that will be added to/from the ring master. Note that inter-node ring delay is set by the ring_inter_node_delay systemverilog output parameter.

RING32 – 32 bit ring interface.

Options:

- dly=N (default 0) - sets the number of additional delay stages that will be added to/from the ring master. Note that inter-node ring delay is set by the ring_inter_node_delay systemverilog output parameter.

The following table shows a comparison of external interface type features:

Ordt allows use of simple verilog expressions (containing bitwise & | ^ ~ operators, shift << >> operators, catenation { } operators, and parentheses) when assigning user defined signals. For example:

signal {} intr1_cntl; // define a new control signal

signal {} intr1_user_enable; // define a new input

// now assign the control using internal state and input...

intr1_cntl = intr1 & intr1_user_enable;

Note that user defined signals are also included in any sv interface wrapper for their defined hierarchy. Also beware that use of user signals to define logic in this way will not be carried to tool outputs such as uvm model.

When declaring a signal for use in the right hand side of a property assignment, the signal declaration should occur prior to the declaration of the left hand side assignment instance.

Use of the string '%instance' in test names/descriptions will be converted to the current instance name.

Ordt allows use of fieldstruct component to define groups of fields/fieldstructs for reuse. For example:

// define a simple fieldstruct

fieldstruct fs1 {

field { sw=rw; hw=rw; we; } fld1[4] = 4'd0;

field { sw=rw; hw=r; } fld2;

};

// define fieldstruct w/ field gaps

fieldstruct fs2 {

field { sw=rw; hw=rw; we; } fld1[3:0] = 4'd0;

field { sw=rw; hw=r; } fld2[8:8];

};

// define fieldstruct w/ an explicit width

fieldstruct fs3 {

fieldstructwidth = 8;

field { sw=rw; hw=rw; we; } fld1[4] = 4'd0;

field { sw=rw; hw=r; } fld2;

};

// define a hierarchical fieldstruct

fieldstruct hier_fs {

fs1 fs1;

field { sw=rw; hw=r; } fld1;

fs2 fs2;

};

// register using these fieldstructs

reg {

hier_fs hier_fs;

fs3 fs3[31:24]; // fieldstruct at a specific bit position

} areg[2];

Ordt adds the following rdl properties:

-

The register category and field sub_category properties are added for jspec flow compatibility. Settings for these properties will be passed to jspec, xml, and uvm model outputs, but will have no effect on generated RTL.

-

The js_attributes property is added to insure jspec attribute setting are preserved when converting between rdl and jspec (as can occur multiple times in an automated flow). js_attributes string values set in rdl will be passed along to generated jspec output as-is, but will have no effect on other generated outputs, including RTL. If js_attributes is defined for a register, this will override automatic calculation of jspec attributes settings from other rdl properties.

-

The js_macro_name, js_macro_mode, and js_namespace properties is added to insure jspec attribute settings are preserved when converting between rdl and jspec. These properties allow a string value to be set in rdl that will be passed as-is to generated jspec output, but will have no effect on other generated outputs, including RTL.

The fieldstructwidth integer fieldstruct property is added to allow a minimum fieldstruct width to be defined.

The hwload field property is added to allow multiple fields to be assigned to specified constant values at the same time using a single common input signal. Multiple hwload inputs can be specified by specifying an integer in parenthesis, hwload(N) = value. For example, in the following code, all fld2 values in all registers will be set to 8'h1 if the h2l_hwload_1 input is driven high.

reg reg1_t {

default reset = 8'hff; // all fields reset to 255

field { } fld1[8]; // fld1 not written by hwload

field { hwload(1) = 8'h1; } fld2[8]; // fld2 written by hwload1

};

regfile rf1_t {

reg1_t reg1;

reg1_t reg2 @0x10;

reg1_t reg3 @0x20;

};

The field maskintrbits property is added to allow an alternate interrupt field behavior when masking/enabling fields. Specifying maskintrbits on an intr field with an enable or mask specified, will cause the enable/mask to modify the value of the field rather than just masking the output intr signal for the register. This feature has use when capturing info that an interrupt has occurred more than once. Note that since the field value is modified by maskintrbits, a halt output specified for this field will also be affected.

For example, the code below with 3 interrupt registers (all 3 intr input signals assumed to driven by the same net) will cause reg1, reg2, and reg3 intr_field to be set on the first, second, and third active cycle of the intr input. Clearing the intr_field bit in reg1 will cause the bit to be cleared in the other 2 registers also.

reg intr_reg {

default reset = 0;

field { sw=rw; hw=na; intr; woclr; } intr_field;

};

intr_reg intr_reg1 @0x100;

intr_reg intr_reg2 @0x200;

intr_reg2.intr_field ->enable = intr_reg1.intr_field;

intr_reg2.intr_field ->maskintrbits = true;

intr_reg intr_reg3 @0x300;

intr_reg3.intr_field ->enable = intr_reg2.intr_field;

intr_reg3.intr_field ->maskintrbits = true;

The rtl_coverage boolean field property is added to allow generation of a toggle coverpoint for specified field values in systemverilog output. All field coverpoints will be added in a single field_cg covergroup.

The satoutput counter boolean field property is added to control generation of saturation output signals when the incrsaturate or decrsaturate options are specified. By default no saturation output indication is generated for a saturating counter.

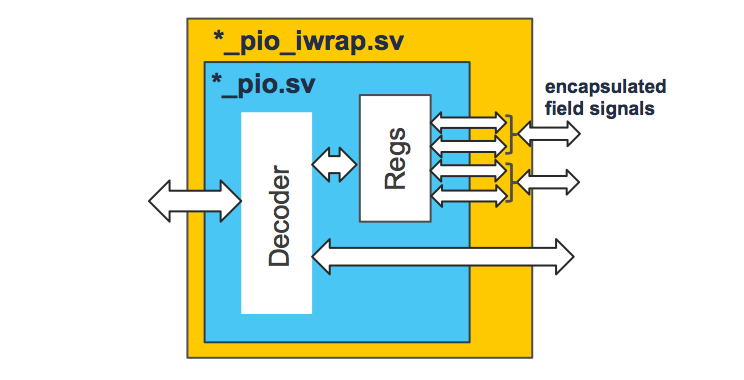

The use_new_interface and use_interface properties are added to allow encapsulation of generated field systemverilog IO signals within systemverilog interfaces. These properties can be applied to regfile, reg, fieldstruct, or field components or instances – if either is specified within rdl input, systemverilog output will include a module named <name>_pio_iwrap that wraps the generated <name>_pio module and converts all field IO signals within the specified hierarchy to an interface that may be accessed externally. use_new_interface will create a systemverilog interface definition having name defined by its rdl instance hierarchy and include this definition in generated systemverilog output. Alternately, use_interface=<intf_name> can be specified to enable use of externally defined interfaces – in this case, no interface definition will be created and the specified <intf_name> will be used in the <name>_pio_iwrap module. By default, new interface/struct definitions will be created for each instance having use_new_interface or use_new_struct specified. The reuse_iwrap_structures ordt control parameter can be used to create only unique structure definitions and reuse these where appropriate.

Similarly, the use_new_struct and use_struct properties are added to allow encapsulation of generated field systemverilog IO signals within systemverilog structs.

The uvmreg_is_mem boolean register property is added to designate that a replicated register should be modeled as a uvm_mem in uvm output to reduce memory footprint. If so designated, the register will be modeled as a uvm_mem with replicated virtual registers rather than multiple uvm_regs.

The uvmreg_prune boolean register property is added to designate that a register should not be added to the generated uvm register model. Any uvm blocks having all child registers specified as uvmreg_prune will also be omitted from the model.

Home

Running Ordt

Building Ordt from source

Running Ordt Tests

Source contributions

Ordt Inputs

Ordt Outputs